# **FACET Cards**

Design Guide

## **Legal Notice**

© 2015 CompuLab Ltd.

All Rights Reserved. No part of this document may be photocopied, reproduced, stored in a retrieval system, or transmitted, in any form or by any means whether, electronic, mechanical, or otherwise without the prior written permission of CompuLab Ltd.

No warranty of accuracy is given concerning the contents of the information contained in this publication. To the extent permitted by law no liability (including liability to any person by reason of negligence) will be accepted by CompuLab Ltd., its subsidiaries or employees for any direct or indirect loss or damage caused by omissions from or inaccuracies in this document.

CompuLab Ltd. reserves the right to change details in this publication without notice.

Product and company names herein may be the trademarks of their respective owners.

CompuLab Ltd. 17 HaYetsira St., Yokneam Elite 20692, P.O.B 687 ISRAEL

Tel: +972-4-8290100 http://www.compulab.co.il http://fit-pc.com/web/ Fax: +972-4-8325251

## **Revision History**

| Revision | Author/Engineer | Revision Changes       |

|----------|-----------------|------------------------|

| 0.99     | Maxim Birger    | Preliminary release    |

| 1.0      | Maxim Birger    | Initial public release |

|          |                 |                        |

|          |                 |                        |

|          |                 |                        |

## **Table of Contents**

| Le | egal No | tice                                   | 2 |

|----|---------|----------------------------------------|---|

| R  | evision | History                                | 3 |

| 1  | Intr    | oduction                               | 5 |

|    | 1.1     | About This Document                    | 5 |

|    | 1.2     | Related Documents                      | 5 |

| 2  | Ove     | rview                                  | 6 |

|    | 2.1     | Scope                                  | 6 |

|    | 2.2     | Concept                                | 6 |

| 3  | FAC     | ET Interface                           | 7 |

|    | 3.1.1   | FACET Electrical Interface             | 7 |

|    | 3.1.2   | FACET Mechanical Interface             | 8 |

| 4  | Exte    | ended Functionality                    | 9 |

|    | 4.1     | PCI Express Interface                  | 9 |

|    | 4.2     | LPC Bus Interface                      | 9 |

|    |         |                                        |   |

| Т  | able    | of Figures                             |   |

|    |         | - FACET Card Concept                   |   |

| Fi | gure 2  | – FACET LAN DXF file                   | 8 |

| Т  | able    | of Tables                              |   |

| T  | hla 1 _ | Mini PCI Express adge connector pinout | 7 |

## 1 Introduction

#### 1.1 About This Document

This document is part of a set of reference documentation necessary to design and program custom FACET Cards for fitlet computers.

#### 1.2 Related Documents

| Document                            | Link                                                  |  |  |

|-------------------------------------|-------------------------------------------------------|--|--|

| PCI express mini card               | http://fit-pc.com/download/facet-                     |  |  |

| electromechanical specification 1.2 | cards/documents/PCI Express miniCard Electromecha     |  |  |

|                                     | nical specs rev1.2.pdf                                |  |  |

|                                     |                                                       |  |  |

| FACET Cards Wiki                    | http://www.fit-pc.com/wiki/index.php/Fit-             |  |  |

|                                     | PC Product Line:FACET Modules                         |  |  |

|                                     |                                                       |  |  |

| FACET FC-LAN reference card         | http://www.fit-                                       |  |  |

|                                     | pc.com/wiki/index.php/FACET_Cards:FC-LAN_Card         |  |  |

|                                     |                                                       |  |  |

| FACET FC-LAN schematics design      | http://fit-pc.com/download/facet-cards/fc-lan/FC-LAN- |  |  |

|                                     | V1_0-Schematics.zip                                   |  |  |

|                                     |                                                       |  |  |

| FACET FC-LAN layout design          | http://fit-pc.com/download/facet-cards/fc-lan/FC-LAN- |  |  |

|                                     | V1_0-Layout.zip                                       |  |  |

|                                     |                                                       |  |  |

| FACET FC-LAN mechanical file        | http://fit-pc.com/download/facet-cards/fc-lan/FC-LAN- |  |  |

|                                     | V1_0-Mechanical.zip                                   |  |  |

|                                     |                                                       |  |  |

| FACET FC-LAN assembly file          | http://fit-pc.com/download/facet-cards/fc-lan/FC-LAN- |  |  |

|                                     | V1_0-Assembly-drawings.zip                            |  |  |

|                                     |                                                       |  |  |

#### 2 Overview

#### 2.1 Scope

FACET Card (Function And Connectivity Extension T-Card) serve as optional extension board providing additional peripherals and IO connectivity options for *fitlet* products. This document outlines FACET Card interface specification and custom FACET Card design guidelines, requirements and recommendations.

#### 2.2 Concept

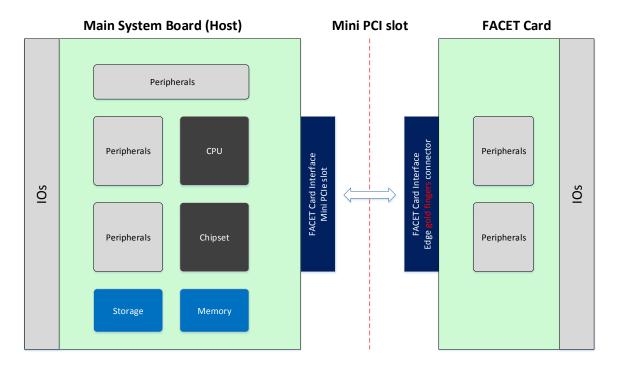

FACET Cards are implemented with internal T-shaped extension board. The extension board is connected to already available motherboard's mini PCI Express slot, featuring standard PC interfaces such as PCIe, USB2, SMBus and LPC Bus.

Figure 1 - FACET Card Concept

## **3 FACET Interface**

#### 3.1.1 FACET Electrical Interface

#### FACET Electrical interface provided in the table below:

Table 1 – Mini PCI Express edge connector pinout

| 1 W 3 P 5 P          | Pin Name  WAKE#  PERn2  PERp2  CLKREQ#  GND  REFCLK-  REFCLK+ | Signal Description  Open drain, active low signal driven low by a mini PCle card to reactivate the PCle link  PCI Express Gen2 differential receive pair 2  Clock request - open drain, active low driven by mini PCle card to request PCle reference clock  Ground connection  Reference clock used to assist the synchronization of PCI Express interface | Pi n#  2  4  6  8  10 | Pin Name  3.3Vaux  GND  1.5V | Signal Description  3.3V power rail  Ground connection  1.5V power rail                  |  |  |  |  |  |

|----------------------|---------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------|------------------------------|------------------------------------------------------------------------------------------|--|--|--|--|--|

| 3 P<br>5 P           | PERn2 PERp2 CLKREQ# GND REFCLK-                               | mini PCle card to reactivate the PCle link  PCl Express Gen2 differential receive pair 2  Clock request - open drain, active low driven by mini PCle card to request PCle reference clock  Ground connection  Reference clock used to assist the                                                                                                            | 6 8                   | GND<br>1.5V<br>LADO          | Ground connection                                                                        |  |  |  |  |  |

| 5 P                  | PERp2  CLKREQ#  GND  REFCLK-                                  | Clock request - open drain, active low driven by mini PCIe card to request PCIe reference clock  Ground connection  Reference clock used to assist the                                                                                                                                                                                                      | 8                     | 1.5V                         |                                                                                          |  |  |  |  |  |

| 7 C                  | CLKREQ#<br>GND<br>REFCLK-                                     | Clock request - open drain, active low driven by mini PCIe card to request PCIe reference clock  Ground connection  Reference clock used to assist the                                                                                                                                                                                                      | 8                     | LAD0                         | 1.5V power rail                                                                          |  |  |  |  |  |

|                      | GND<br>REFCLK-                                                | by mini PCIe card to request PCIe reference clock  Ground connection  Reference clock used to assist the                                                                                                                                                                                                                                                    |                       |                              |                                                                                          |  |  |  |  |  |

| 9 G                  | REFCLK-                                                       | Reference clock used to assist the                                                                                                                                                                                                                                                                                                                          | 10                    | LADA                         | 1                                                                                        |  |  |  |  |  |

|                      |                                                               |                                                                                                                                                                                                                                                                                                                                                             |                       | LAD1                         | LPC Bus Data signals                                                                     |  |  |  |  |  |

| 11 R                 | REFCLK+                                                       | synchronization of PCI Express interface                                                                                                                                                                                                                                                                                                                    | 12                    | LAD2                         |                                                                                          |  |  |  |  |  |

| 13 R                 |                                                               | timing circuits                                                                                                                                                                                                                                                                                                                                             | 14                    | LAD3                         |                                                                                          |  |  |  |  |  |

| 15 G                 | GND                                                           | Ground connection                                                                                                                                                                                                                                                                                                                                           | 16                    | LFRAME#                      | LPC Bus frame signal. Active Low.                                                        |  |  |  |  |  |

| Mechanical Notch Key |                                                               |                                                                                                                                                                                                                                                                                                                                                             |                       |                              |                                                                                          |  |  |  |  |  |

| 17 P                 | PETn2                                                         | ····Condi                                                                                                                                                                                                                                                                                                                                                   | 18                    | GND                          | Ground connection                                                                        |  |  |  |  |  |

|                      | PETp2                                                         | PCI Express Gen2 differential transmit pair 2                                                                                                                                                                                                                                                                                                               | 20                    | MPCIEO_DIS# /<br>W_DISABLE#  | Active low signal when asserted by the system disable PCIE/radio operation.              |  |  |  |  |  |

| 21 G                 | GND                                                           | Ground connection                                                                                                                                                                                                                                                                                                                                           | 22                    | PERST#                       | Asserted when power is switched off and also can be used by the system to force HW reset |  |  |  |  |  |

| 23 P                 | PERn0                                                         |                                                                                                                                                                                                                                                                                                                                                             | 24                    | 3.3Vaux                      | 3.3V power rail                                                                          |  |  |  |  |  |

| 25 P                 | PERpO PCI Express Gen2 differential receive pair 0            |                                                                                                                                                                                                                                                                                                                                                             | 26                    | GND                          | Ground connection                                                                        |  |  |  |  |  |

| 27 G                 | 7 GND Ground connection                                       |                                                                                                                                                                                                                                                                                                                                                             | 28                    | 1.5V                         | 1.5V power rail                                                                          |  |  |  |  |  |

| 29 G                 | GND                                                           | Ground connection                                                                                                                                                                                                                                                                                                                                           | 30                    | SMB_CLK                      |                                                                                          |  |  |  |  |  |

| 31 P                 | PETn0                                                         |                                                                                                                                                                                                                                                                                                                                                             | 32                    | SMB DATA                     | Optional SMBus two-wire interface for Host/mini PCIe module communication                |  |  |  |  |  |

|                      | PETp0                                                         | PCI Express Gen2 differential transmit pair 0                                                                                                                                                                                                                                                                                                               | 34                    | GND                          | Ground connection                                                                        |  |  |  |  |  |

|                      | GND                                                           | Ground connection                                                                                                                                                                                                                                                                                                                                           | 36                    | USB_D-                       |                                                                                          |  |  |  |  |  |

|                      | LPC CLKO                                                      | LPC Bus clock                                                                                                                                                                                                                                                                                                                                               | 38                    | USB D+                       | USB Host Interface                                                                       |  |  |  |  |  |

|                      | 3.3Vaux                                                       | 3.3V power rail                                                                                                                                                                                                                                                                                                                                             | 40                    | GND                          | Ground connection                                                                        |  |  |  |  |  |

|                      | 3.3Vaux                                                       | 3.3V power rail                                                                                                                                                                                                                                                                                                                                             | 42                    | LED_WWAN#/ LPC_SMI#          |                                                                                          |  |  |  |  |  |

|                      | PETn1                                                         |                                                                                                                                                                                                                                                                                                                                                             | 44                    | LED_WLAN#/ LPC_PME#          | Active low output signals are provided to                                                |  |  |  |  |  |

|                      | PETp1                                                         | PCI Express Gen2 differential transmit pair 1                                                                                                                                                                                                                                                                                                               | 46                    | LED_WPAN#/ SERIRQ            | allow status indications to users via system provided LEDs (or LPC Bus control signals). |  |  |  |  |  |

|                      | LPC RST#                                                      | LPC Bus Reset signal. Active Low.                                                                                                                                                                                                                                                                                                                           | 48                    | 1.5V                         | 1.5V power rail                                                                          |  |  |  |  |  |

|                      | PERn1                                                         |                                                                                                                                                                                                                                                                                                                                                             | 50                    | GND                          | Ground connection                                                                        |  |  |  |  |  |

| 51 P                 | PERp1                                                         | PCI Express Gen2 differential receive pair 1                                                                                                                                                                                                                                                                                                                | 52                    | 3.3Vaux                      | 3.3V power rail                                                                          |  |  |  |  |  |

FACET Card interface based on regular mini PCI Express interface featuring extended signals and functionality, as legacy LPC Bus interface and additional PCI Express lanes.

#### 3.1.2 FACET Mechanical Interface

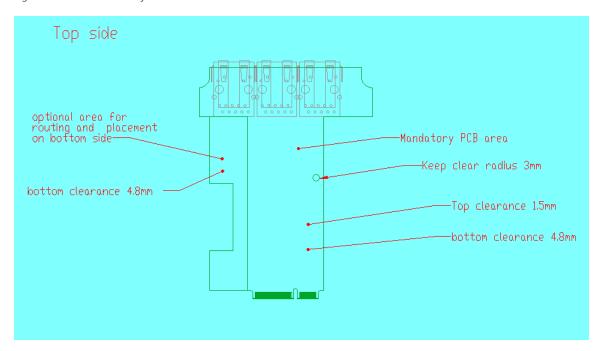

As noted in the previous section, FACET interface based on standard mini PCI express connection, electrical as well as mechanical, meaning all mechanical and layout guidelines apply for FACET mechanical design.

PCB shape of custom FACET derived from fitlet-X PCB design, mechanical stack-up and other mechanical constraints, shown in the DXF file below. The file can be downloaded from product wiki portal.

Figure 2 - FACET LAN DXF file

FACET PCB design should meet mini PCI Express design guidelines in terms of edge connector design (hard gold fingers), PCB thickness, other parameters, and follow general recommendations described in PCI express mini card electromechanical specification 1.2.

## 4 Extended Functionality

#### 4.1 PCI Express Interface

Fitlet-X SoC provides several PCI Express Root Ports, supporting the PCI Express Base Specification, Revision 2.0. Each Root Port lane supports up to 5 Gbps bandwidth in each direction (10 Gbps concurrent). FACET PCI Express interface consist of 3x PCI Express gen2.0 lanes.

#### 4.2 LPC Bus Interface

The Low Pin Count (LPC) bus interface is a cost-efficient, low-speed interface designed to support low-speed legacy (ISA, X-bus) devices. The LPC interface essentially eliminates the need of ISA and X-bus in the system. Here the ISA bus is internal to SoC and is used for connecting to the legacy Direct Memory Access (DMA) logic. The LPC host controller is integrated into the SoC. It connects to the internal A-Link bus on one side and the LPC and Serial Peripheral Interface (SPI) buses on the other side. The ISA interface is only used for legacy DMA operation.

Examples of LPC devices include Super I/O (disk controller, keyboard controller), BIOS RAM, audio, Trusted Platform Module (TPM), and system management controller.

LPC host controller has the A-Link bus on one side and the LPC bus on the other. The host controller supports memory and I/O read/write, DMA read/write, and bus master memory I/O read/write. It supports up to two bus masters and seven DMA channels.